## BMS INSTITUTE OF TECHNOLOGY AND MANAGEMENT

Avalahalli, Doddaballapura Main Road, Bangalore - 560064

#### **Electronics and Communication Engineering**

**Subject: ARM and Embedded System**

**Code: 17EC62**

#### **Table of Contents**

| Sl.No | Modules | Page.No |

|-------|---------|---------|

|       |         |         |

| 1     | 1       | 1-13    |

|       |         |         |

| 2     | 2       | 14-38   |

|       |         |         |

| 3     | 3       | 39-78   |

|       |         |         |

| 4     | 4       | 79-92   |

|       |         |         |

| 5     | 5       | 93-126  |

|       |         |         |

#### ARM-32 BIT MICROCONTROLLER

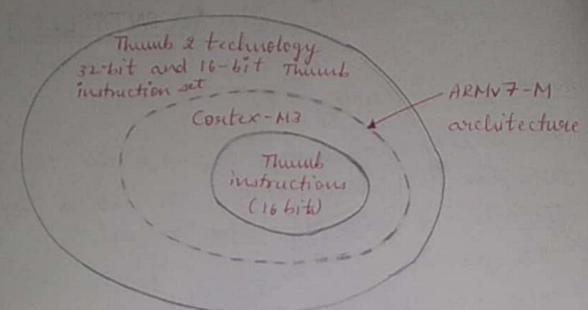

## Thumb 2 Jechnology

- The Thumb-2 technology extended the Thumb, Instruction set Anchitecture (15A) into a highly efficient and powerful instruction set,

- -> This provides the benefits of ease of use, code size and good performance.

- -> Here 32-bit instructions set can be split into 16-bit instruction sets.

- This allows more complex operations to be carried out in an efficient way by reducing the number of states switching between ARM state and Thurb state.

- → Cortex-M3 supposets only Thumb-2 Instructional set.

- For the first time, hardware divide instruction set is available on an ARM Processer and certain other instructions are available to improve datacrunching penformance.

- > 9t also supposits analigned data accesses which was available only in high-end processors before.

Fig 1: Relationship between the Thumb Instruction Set in Thumb-2 Technology and the Traditional Thumb.

## CORTEX-M3 PROCESSOR APPLICATIONS

I dow-cast microcontrollers:

- \* Costex-M3 processor is ideally suited for low cost unicrocontrollers.

- + These are commonly used in consumer products from toys to electrical appliances.

- + Its lower power, high performance and ease of use advantages enabled to develop products with

- 2) Automotive electronics:

- \* Another ideal application of Cortex-M3 processes

- + It has high performance efficiency and low interrupt latency which allows it to use in seal-time systems + It supposets upto 240 external rectored interrupts.

- 3) Data Communications:

- \* The processor's low power consumption, high efficiency and thumb-2 technology usage for lift manipulations makes CORTEX-M3 more ideal and compatible for many communications applications like Blue tooth.

#### 4) Industrial Control:

- \* In industrial control applications simplicity, fast response and reliability are key factors.

- \* Its low interrupt latency and enhanced faulthandling features make it strong in this area

- 5) Consumor Products:

- \* In many consumer products, a high penformance

- + Again its interrupt feature and enhanced fault handling ability makes it strong cornelidate in this area.

- + It supports an MPV enabling complex software to execute while providing memory protection.

PTO

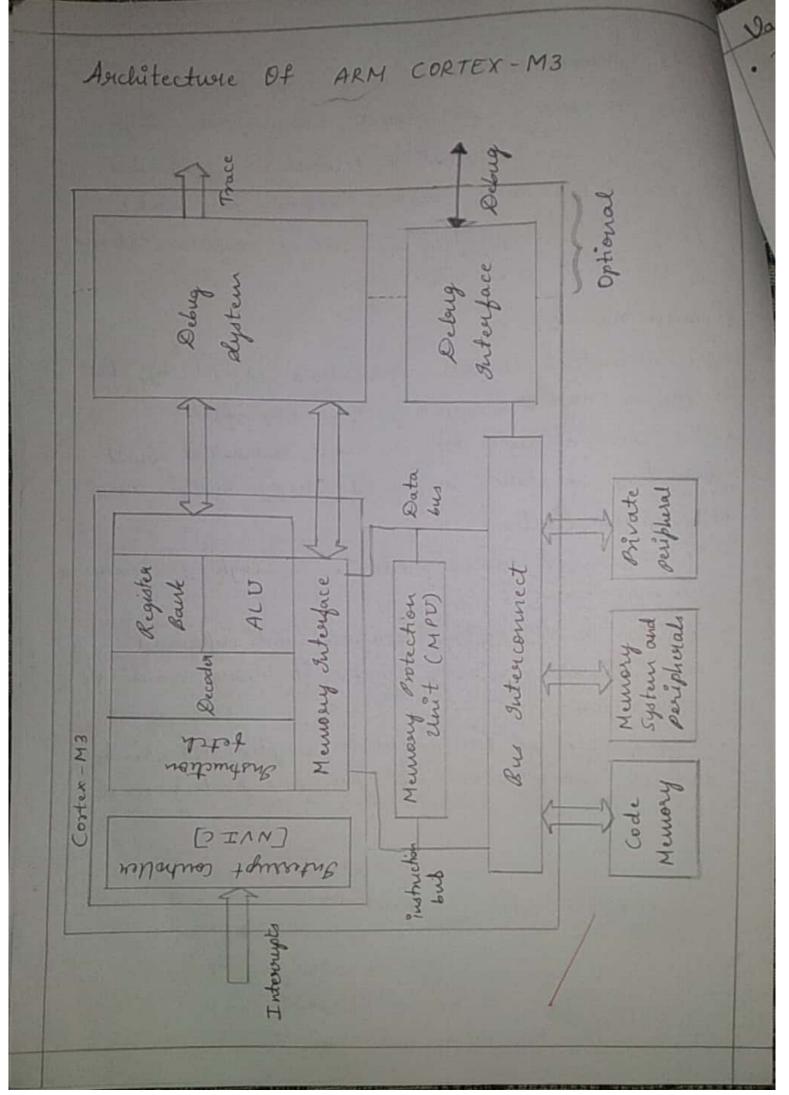

Vasious Elvits in the Anchitecture

· The Courtex-M3 processor is a 32-bit processor with 32 bit wide data path, register bank and minory interface.

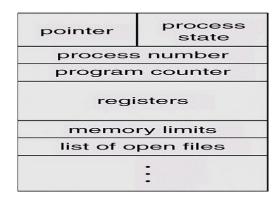

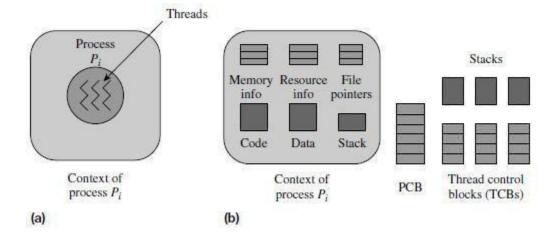

· Register Bank: There are 13 general purpose registeres, two stack pointers, a link register, a program counter and program status engisted

So in total it has 16 sugestees

· Decoden: - Contex-M3 processors has a decoder for Thumb & Instructions and also traditional Thumb inshuctions

· ALU: It has an advanced ALV with supposet of hardware multiply and divide, control logic,

· Memory Juterface: Cortex - M3 is a memory mapped system with a simple, fixed memory map for up to 4 gigalytes of addressable memory. which has predefined, dedicated addresses for code There is also a special segion to provide for vendos specific addressability.

· MPU: It is an optional component of contex-M3 processed that can improve the reliability of an embedded system by protecting critical data used by the os from user applications.

- Helps in separating processing tasks by disallowing access to each other's data, allowing mentary segions as sead-only and detecting unexpected memory access

- Interrupt Controller (NVIC): This NVIC is highly configurable It provides very good (or) outstanding interrupt handing abilities to the processor. It supplies NMI and 32 general purpose Physical interrupts with 8 sevel precuption priority.

- Debug System: The delay access into a Coster M3 processed based system is through the Debug Access Post (DAP) that can be implimented with JTAG on SW protocol

- · The processar has separate instruction bus and data bus.

- where code is stored, memory system and other peripherals and also to other private peripherals.

- The processor low matrix connects the processor and debug Interface to the external buses. It has 32-bit AMBA interfacing bus. It can be further divided into AHB and APB AHB Advanced High speed Bus.

APB Advanced Peripheral Bus.

- · The lows matrix also implements unaligned data accesses and bit bounding

#### General Purpose Registers > Costex - M3 Processor has 13 general purpose registeers from Ro to R12 -> All are 32 - bit registers for data operations Registers in CORTEX - N3 Ro RI R2 dow R3 Registers R4 General R5 Purpose Ro Legisters Ry RE Ra High Rio registers RI Rn R 13 -> Stack Pointer (SP) Special R14 -> Linke register (LE) Registers RIS -> Program Counter (PC) Special Registers in Register Bank O R13 - Stack Pointers -> Costex-M3 has 2 stack pointers but only one is visible at a time -> MSP and PSP are the two stack pointers

- Hair Stak Pointen (MSP); The default stack pointer, used by the operating system (os) kennel and exception handless - The data is stoned , pushed and poped out automatically -> Freces Stack Pointer (PSP): Used to application code and in priviledge mode - The lowest & Bits of Hack pointers are always o , which means they are always word aligned @ R14 The Kink Register when a subsoutine is called, the extrum address is steered in the link register instead of stack -> FIB - Fast interrupt request is used sometimes instead of IRB but not in Cortex M3 -> Here the laterry is deaned. 1 R15 Program Counter -> 94 a 32- bit negisten which helds the address of next instruction supposed to be executed - The register can be written to control the program flow Other Special Registers. · Program Status registers (PSRs) · Interrupt Mask aggisters (PRIMASK, FAULTHASK, BASEPRI) · Control negister (CONTROL)

| Registers                                  | Functions                                                                                                                                                                                            |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPSR<br>SEPSR<br>SAPSR<br>SIPSR<br>PRIMASK | Provide anithmatic and logic processing flags (ZF &CF) execution status and current executing interrupt number.  Disable all interrupts except NMI and hard fault  Disable all interrupts except NMI |

| · BASEPRI                                  | Disable all intercupts of specific priority level on lower priority level                                                                                                                            |

| ·CONTROL                                   | Define privileged status and stack pointer selection.                                                                                                                                                |

- -> cortex M3 has a number of debugging features. such as program execution contends, including halting and stepping, instructions breakpoints, data watchpoints, registers and memory accesses.

- -> The debugging hardware is based on Coresight auchitecture.

- -> Unlike traditional ARM, the CPU come itself does inot have JTAG interface. Instead a delong interface module is idecoupled from case and bus intenface DAP is provided at core level.

- The control of this interface is carried out by a Deleng Post (DP) device. The deleng host can collect the executed instruction info" via external trace capturing hardware.

| Interrupts | and | Exc | eptions. |

|------------|-----|-----|----------|

|------------|-----|-----|----------|

| -                |                        | 4            |                                                                                                          |

|------------------|------------------------|--------------|----------------------------------------------------------------------------------------------------------|

| Exception Number | Type of Exception      | Priority     | Functions / Descriptions                                                                                 |

| 0                | NA                     | NA           | No exception enuring                                                                                     |

| 1                | Reset                  | -3 (Hyliest) |                                                                                                          |

| 2                | NMI                    | - 2          |                                                                                                          |

| 3                | Hand fault             |              | Non Maskable interrupt<br>(external NMI input)  All fault conditions, if the corresponding fault handler |

| 4                | Memory<br>Manage fault | Programmable | not enabled.  MPU violation on access to illegal                                                         |

| 5                | Bus fault              | Programmable | 1 1000 7700                                                                                              |

| 6                | Usage fault            | - "-         | data about<br>Program error                                                                              |

| 7-10             | Reserved               | NA           | Reserved                                                                                                 |

| 11               | SV Call                | Programmable | Supervison Call                                                                                          |

| 12               | Debug Monitor          | - 11 -       | break points, match points                                                                               |

| 13               | Reserved               | NA           | external debug request                                                                                   |

| 14               | Pend SV                | Programmable | Reserved<br>Pendable request for                                                                         |

| 12               | sy stick               | - u —        | System Seavice<br>Pendable sequest for                                                                   |

| 16               | IR8#0                  | - u -        | External interrupt #0                                                                                    |

| 255              | IRQ#239                | - "          | External interrupt # 239                                                                                 |

> Contex-M3 implement new exception model which is introduced in ARM 17-M anchitecture -> This is different because it has enabled very efficient exception handling also muster of system exception handling -> It also has external Interrupt request (IRB) -> No FIB in the Copter N3 but it supposits nested interrupt hence it is easy to set up a system. Stack Operation. -> Stack is a Memory mage model - It is simply a part of system memory -> The stack operations are as follows STACK PUSH OPERATION STACK POP OPERATION Register contents Data PUSH Processing POP Register contents nestored Memory Memory -s In Contex - M3, the instructions you accessing stack memory are PUSH and POP. The yestax is as to llouis PUSH (ROZ; R13=R13-4, then Memory [R13] = RO POP FROY; RO = Memory (R13), then R13 = R13+4

-> Costex -M3 has a predefined memory map.

-> This allows the built in peripherals, like interrupt controller and delong components to be accessed by simple instructions.

-> Thus most of it is accessible in congram code.

-> Memory map allows processor to be highly optimized for speed and ease of integration in system -on-a chip designs

differently. I. e the data can be put in cost region and code in RAM segion.

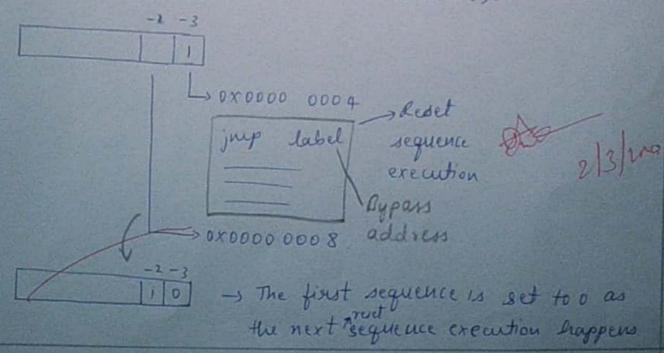

Reset Sequence.

-> After the processor exits nesel, it will read two words from memory

· Address 0x00000000 : Stauting value of R13 (SP)

· Address 0x00000004: Reset vector

(stanting address of program execution; LSB should be set to 1 to indicate thumb state).

## MODULE - 02

# ARM CORTEX M3 INSTRUCTION SETS AND PROGRAMMING

This is the introduction of some basic syntax of ARM assembly to make it easier to understand the nest of the code in the following sections.

Assembler language: basic Syntax

In assembler ade, the following instruction formating is sommonly used

label opcode operand, operand 2 . - .; Comments.

-> The label is optional.

-> some instructions may have it so that the address of instruction can be determined using the label.

-> Then we will find the opcode (instruction) and number of operands

> Normally the 2st openand is destination operand >> Sometimes the syntax formate for operand can

also be different. For example, immediate

data are usually in the form # number,

as shown below:

MOV RO, # 0x12; Set RO = 0x12 (haxadecimal)

MOV RI, # 'A'; Set RI = ASCII character A

- Note that the text after each suricolon is comment .

They donot affect the program operation but they make us easien to understand.

- -> For defining constants we use EQU and then we can use those constants inside program code. For example:

NVIC-IRA-SETENO EQU OXEDDOEIDO NVIC-IRAD-ENABLE EQU OXI

LDR RD, = NVIC - IRB - SETENO; LDR here is a

; instruction that convert

; to a pc relative load by

; assembler.

MOV RI, #NVIC-IRGO\_ENABLE; Move immediate data to register str. RI, [RO]; Enable IRB 0 by writing; RI to address in RD.

- -> We have number of lata definition directives used for insertion of these constants inside code one such is DCI (Define Constant Instruction)

- This DCI can be used to code the instruction when our assembler cannot generate the exact instruction that we want and if the binary code of the instruction is known.

DCI OxBEDD; Breakpoint (BKPT 0), a 16-bit instruction.

- -> We have DCB (Define Constant Byte) for byte size constant values

- -> Then DCD (Define constant data) for word rize constant values to define binary data in our code

Example: LDR. R3, = MY\_NUMBER; Gret memory address value of MY\_NUMBER LDR Rq, [R3] Get the value code. 0x12345678 in R4 ; Get the starting memory LDR RD, =HELLO - TXT address of HELLO-TXT BL Point Text ; call a function called ; PrintText to display string MY-NUMBER DCD 0x12345678 HELLO\_TXT DCB "Helloin", 0; mill terminated string -> Note that the assembler syntax depends on which assembler tool we are using Assemblea danguage: Use of Suffixes In assembler for ARM processous, instructions can be followed by suffixes, as shown in Table. -> For Branch instructions we use conditional execution suffixes in Cortex-M3 But other instruction can also use conditional execution suffixes if they are inside an IF-THEN instruction block Suffix Description update Application Program Status register (APSR) (flags) Eg. ADDS RO, RI; this will update APSR EQ, NE, LT, GT Conditional execution; Eg= Equal, NE=Not equal and so on. LT = dess than, GT = Greater Than and so on For example; BEB < Label > ; Branch if equal

## Assembles language : Unified assemblen language

The Unified Assembler language (UAL) is developed to allow delection of 16-bit and 32-bit instructions.

Ext ADD RO, RI; RO-RO+RI, using Traditional Thumb ADD RO, RO, RI; Equivalent instruction syntax; using UAL syntax

Traditional Thumb instruction change the flags in APSR, even if the Souffix is not used.

-> when VAL syntax is used the instruction changes the flag depending on the Souffix.

Ex:

ADDS RO, #1; Use 16-bit thumb instruction by default for smaller size

ADDS.N RO, #1; Use 16-bit Thurs instruction (N= Marrow) ADDS.W RO, #1; Use 32-bit Thurb instruction (W= wide)

>94 must cases c compilers will be 16-bit instruction if passible due to smaller code size. However, when the immediate data exceed a certain range on when the operation can be better handled with a 32-bit Thumb-2 instruction the 32-bit instruction will be used.

Ex:

AND RO, RI; Equivalent UAL Syntax (5 suffix is added) with the new instructions in thumb-2 technology, some of the operations can be handled by either Thumb instruction (or) a Thumb-2 instruction.

| I | N | 5 | T | R | U | C | T | IDN | 1 | LI | S | T |

|---|---|---|---|---|---|---|---|-----|---|----|---|---|

| - | _ | - | _ | - | - | - | _ |     | - | -  | _ | _ |

| 16 - 6"t | Data | Processing | Instructions |

|----------|------|------------|--------------|

|          |      |            |              |

| Instruction | Function.                                        |

|-------------|--------------------------------------------------|

| ADC         | Add with carry                                   |

| ADD         | Add                                              |

| ADR         | Add PC and an immediate value of put the         |

|             | result in a register                             |

| AND         | logical AND                                      |

| ASR         | suffematic shift eight                           |

| BIC         | Bit clean ( logical AND one value with the logic |

|             | inversion of the other)                          |

| CMN         | Compare Negative                                 |

| CPY         | copy (Synonym of MOV instruction)                |

| EOR         | Exclusive OR                                     |

| LSL         | Legical shift left                               |

| LSR         | Logical shift right                              |

| MOV         | Move (can be used for register - register on     |

|             | loading immediate data)<br>Multiply              |

| MUL         | Multiply                                         |

| MUN         | More NOT Coltain logical invested value)         |

| NEG         | Negate Cobtain 2's complement value),            |

|             | equivalent to RSB                                |

| ORK         | logical DR                                       |

| RSB         | reverse subtract                                 |

| ROR         | Lotate night                                     |

| SBC         | Subtract with carry                              |

| SUB         | Subtract                                         |

| TST         | Test (use logical AND, 2 flag updated but        |

|             | AND result is not stored)                        |

| REVIG       | Revuse the bute order:                           |

|             | Reverse the byte order in each 16-bit half       |

| REV         | word of a 32 - 61+ register.                     |

| FEV         | leverse the byte order in 32-5it register.       |

|             | REVSH<br>SXTB<br>SXTH | Revuese the byte order in the lower 16-58t.  Aulf word of a 32-68t segester and sign extend  the should to 32-68ts  Signed extend Byte  Signed extent half word |

|-------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | DYTE                  | uniqued extend byte                                                                                                                                             |

|             | UXTH                  |                                                                                                                                                                 |

|             | UXII                  | clasigned extend half word                                                                                                                                      |

|             | 16 - bit              | Branch Fustriction                                                                                                                                              |

| 1           | Instruction.          | Function                                                                                                                                                        |

|             | 6                     | Branch                                                                                                                                                          |

|             | Becounds              | conditional branch                                                                                                                                              |

|             | BL                    | Branch with link; call a Subsoutine of store return                                                                                                             |

|             | BLX                   | Branch with link of change state (Bex < reg >outy)                                                                                                              |

|             | Bxcregz               | Branch with exchange state                                                                                                                                      |

|             | CBZ                   | Compasse and branchif zero                                                                                                                                      |

|             | CBNZ                  | Compasse and branch if non-coro.                                                                                                                                |

|             | ₹T                    | 9f - their                                                                                                                                                      |

|             | 16-bit                | lead and store Instructions.                                                                                                                                    |

|             | Instruction           | Function.                                                                                                                                                       |

|             | LDR/H/8               | load word from memory to register / half wood/syte                                                                                                              |

|             | LOR SH                | cood half word from munory, sign extend it,                                                                                                                     |

|             |                       |                                                                                                                                                                 |

|             | LOK 5B                | Good byte from memory, sign extend it, put                                                                                                                      |

|             |                       | I In regulation.                                                                                                                                                |

| 1           | STE/H/B               | Store word/ Half word/ Lyte from against to                                                                                                                     |

| 1           |                       | memory                                                                                                                                                          |

| 1           | LOM/LONIA             |                                                                                                                                                                 |

| The same of | STMISTMIA             | Store multiple las                                                                                                                                              |

|             | PUSH                  | Push multiple register                                                                                                                                          |

|             | POF                   |                                                                                                                                                                 |

|             |                       | Pop multiple register.                                                                                                                                          |

|             |                       |                                                                                                                                                                 |

| Instruction | Function                                                                                                                                                                    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SVC         | Supervisor Call                                                                                                                                                             |

| SEV         | sand event                                                                                                                                                                  |

| WFE         | sleap and wait for event                                                                                                                                                    |

| WFI         | Sleep and wait for interrupt.                                                                                                                                               |

| BKPT        | areakpoint; if delay is enabled, it will enter delay mode (halted) or if delay monitor exception enabled, invoke delay exception; otherwise it will invoke fault exception. |

| CPSIE       | Enable PRIMASK (CASIE i) / FAULTMASK (CASIE +)                                                                                                                              |

| CPSID       | Disable PRIMASK (CPSIE i)/FAULTMASK (CPSIE f) register (set the register to 1)                                                                                              |

#### INSTRUCTION DESCRIPTION

Assembler Language: Moving Data

- The most basic functions in a processor is transfer of data.

Data transfer can be one of the following types

· Moving data between stegister and register.

· Moving data lecturen memory and register.

· Moving data between special register and register.

. Moving an immediate data value into a register.

The command to move data value between register is MOV Ex: MOV R8, R3

The basic instruction for accessing munory are load of

Load (LDR): transfers data from memory to registers

Store transfers data from registers to memory

Ex:

STMIA.W R8!, {Ro-Roy; R8 changed to 0x8010 after store (increment by 4 words)

STMIA W R8, SRO-R3 y; R8 unchanged after store.

SThe exclamation mark [!) in the instruction specifies whether the register Rd should be updated after the instruction is completed.

Ex: LDR.W RO, [RI, # offset]!; Read memory [RI+offset], with R, update to RI+offset.

-> Two other types of memory operations are stack push and stack pop.

PUSH {RD, R4-R7, R93; Push Ro, R4, R5, RC, R7, R9 into Stack memory

POP {R2, R3} ; Pop R2 and R3 from stack.

to access these registers, we use MRS and MSR instruction

Ex: MRS RD, PSR ; Read Processes status word into RD

MSR CONTROL, RI; Write value of RI into control register

Assembler Language; Processing Data

The coertex -M3 provides many different instructions for data processing.

Addition operation

Ex: ADD RO, RO, RO; RO = RO+P1

ADDS RO, RO, #0x12; RO = RO+0x12

ADD. W RO, RI, RZ ; RO-RI+RZ (Flag unchanged) ADDS.W RO, RI, RZ ; Flags change. Multiplication 32 bit instruction SMULL RdLO, RdHi, Rn, Rm; [RdHi, RdLO] = Rn+Rm 132-bit multiply instruction for signed UMLAL ROLD, Rolli, Rn, Rm; [RdMi, RdLo]+=Rn+Rm L> 32-bit multiply instruction for unsigned Legic Operation Instruction -> AND Rd, Rn; Rd = Rd & Rn Bitwise AND -> ORR. W Rd, Kn, #inmed; Rd = Rn /# inmed Bitwise DR -> BIC.W Rd, Rn, Rm; ld = Rn f(nRd) Bit clease -> DRN. W Rd, Rn, # inmed; Rd = Rn / (n# inmed) Bitwise OR NOT -SEOR Rd, Rn ; Rd = Rd ^ Rn Bitwise Exclusive OR Shift and Rotate Instructions: -> ASR Rd, Rn, #inmed; Rd= Rn>simmed (Arthumatic shift right) -> LSL Rd, Rn ; Rd = Rd CCRn, (dogical shift left) -> LSR Rd, Rn, Rm; Rd = Rn >> Rm (legical shift right) -> ROR Rd, Rn; Rd rot by Rn (Rotate ought) -> RRX.W Rd, Rn; &C, Rdy = {Rn, C} (Rotate right extended) Logical Shift Left (LSL) C Registers 0 logical Shift right (LSR) 0 -> Register >C

#### Assembler Language: Call and Unconditional Branch

Blakel; Branch to a labeled address

Br reg ; Branch to an address specified by a register.

-> Flag Bits in APSE that can be used for conditional Branches.

| Flag | PSR Bit | Description.  |

|------|---------|---------------|

| N    | 31      | Negetive flag |

| 2    | 30      | zero play     |

| C    | 29      | carry tlag    |

| V    | 28      | overflow flag |

#### Other Instructions:

-> CMD Ro, RI; Calculate RO-RI and update flag.

CMD RO, #0x12; Calculate RO-0x12 and update flag

-> CHN RO, RI; Calculate RO - (-RI) & update flog.

-> TST RO, RI; Calculate RO AND RI & update flag.

#### USEFUL INSTRUCTIONS

#### 1) MSR and MRS

These two instructions provide access to the special register in the coestex M3.

#### Syntax!

MRS < Rn>, (sleg); Move from special Register

MSR < Skeg>, (Rn>; Hoite to special Register

Ex: To set up the process stack pointed

LDR RO, = 0x 20008000; new value for Process Stack

MSR PSP, RO

Pointeu (PSP)

- 2) More on the IF THEN Shatruction

Conditional Execution using IT instruction.

The IF-THEN (IT) instruction allow up to four succeeding instructions (called an IT block) to be conditionally executed.

- · < x> specifies the execution condition for the

- · <y> specifies the execution condition for the third

- · < 2> specifies the execution condition for the fourth

- · cond > specifies the base condition of the instruction block.

Ex:

IT ES \_\_\_\_ only one conditional instruction

ADDES RO, RD, RI

ITE GE

ADDET RO, RO, RI -> Two conditional instructions

ADDLT RO, RO, R3

ITET -> Three conditional instruction

ITETT -> four conditional instruction.

#### 3) SDIV and UDIV

Syntax for signed and uniqued divide instructions

Spiv. W < Rd), < Ru), < Rm)

UDIV. W < Rd>, < Pn>, < Rm>

The result is Rd = Rn/Rm

Ex: LDR RD, = 300; Decimal 300

MOV RI, #5

VDIV.W R2, R0, R1; 12 = 60 (0x3c)

set up the DIVBYZERO bit in the NVIC configuration control Register so that when a divide by zero occurs a fault exception takes place, else < Rd > will become o if a divide by zero takes place.

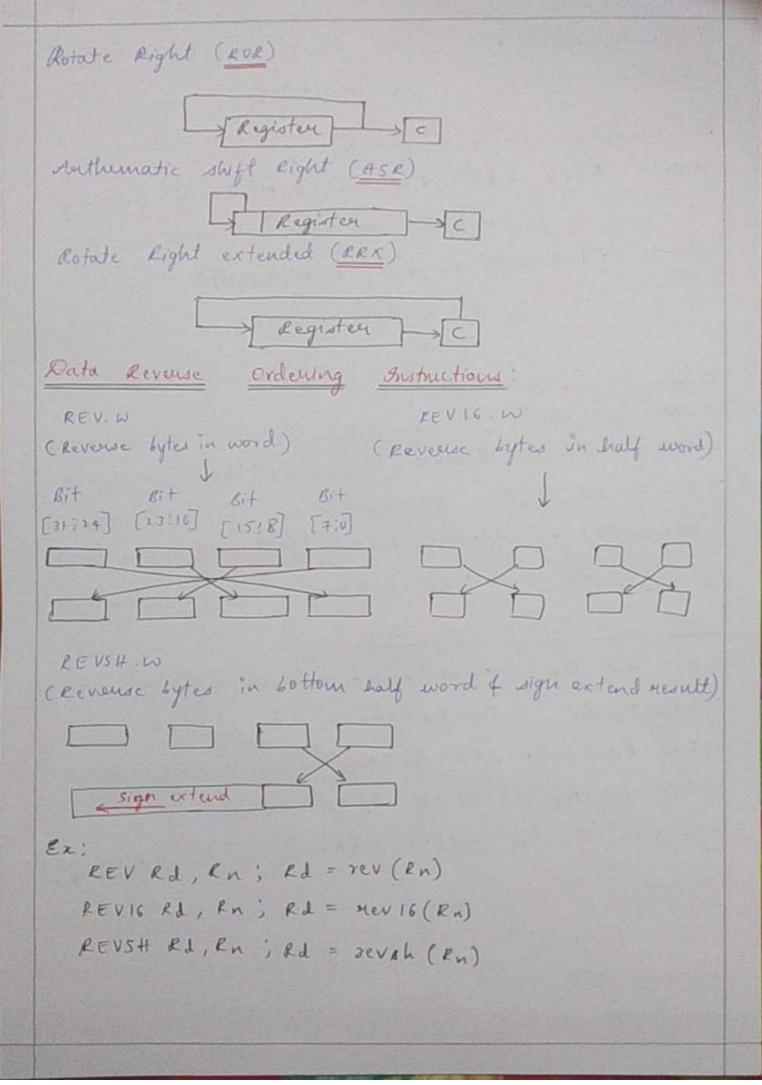

### 4) REV, REVH, and REVSH

REV severses the byte order in a data word REVH reverses the byte order inside a half word REVSH reverses the Lyte in Lottom half word and is sign extended.

Ex: 9/ RD-0 x12345678

REV RI, LO ; RI = 0×78563412

REVH R2, RD; R2 = 0x34127858

REVSH RI, RO; 9/ RD = 0x33 448899

R1 = 0xFFFF9988

#### 5) Revelse Bit

The RBIT instruction reverses the bit order in a data.

Syntax: RBIT , W < Rd>, < RN>

Ex: 9/ RO = 0x84 E10 C23 (1011 - 0100 - 1110 - 0001 0000 \_ 1100 - 0010 RBIT, WRO, RI

lo will become 0x C+ 3 08 7 28 (1100 \_0100 \_0011 \_0000 \_1000 \_0111 \_0010)

## 6) SXTB, SXTH, UXTB, WXTH

The 4 instructions are used to extend a byte on half word data into a word.

PTO -

Syntax:

SXTB <Rd>, <Rn> 3 data one sign extended

SXTH <Rd>, <Rn> Jusing 6i+ [7]/6i+ [15] of Rn

UXTB <Rd>, <Rn> J. the value is 0 extended

UXTM < Rd>, <Rn> J. the value is 0 extended

UXTM < Rd>, <Rn> J. to 32-6i+.

Ex: RD = 0x55 AA 8765

SXTB RI, RO; RI =  $0 \times 000000065$ SXTH RI, RO; RI =  $0 \times FFFFF = 8765$ UXTB RI, RD; RI =  $0 \times 00000065$ UXTH RI, RD; RI =  $0 \times 00000065$

7) Bit Field Clean and Bit Field Insent.

in any position of a segester.

Syntax: BFC.W < Rd>, <# 15b>, <# width>

Ex:

LDR RO, = 0x1234FFFF

BFC W RD, #4, #8 // RD = 0x123 + FODF

Bit Field insent (BFI) copies 1-31 bits (# width)

from one register to any weation (#1x6) in another register

Syntax: BFI.W < Rd>, < Rn>, < #1xb>, < # width>

Ex: LDR RO, = 0×12345678

LDR RI, = 0×3355AACC

BFI.W RI, RO, #8, #6; Insent Ro [15:0] to

RI[R3:8]

:.RI=0×335678CC

8) UBFX and SBFX UBFX and SBFX are the unsigned of signed bit field extract instruction Ex: LDR RD, = 0x5678ABCD ; R1 = 0x000000BC UBFX.W R1, R0, #4,#8 ; RI = OXFFFFFFBC SBFX.W R1, RD, #4, #8 9) LDRD and STRD These two instructions transfer two words of data from on into two registers. Ex: LDR RZ, = 0x1000 LPRD. W RO, RI, [R2]; RO = memory [0x1000] ; R1 = memory [0x1004] STRD.W RO, RI, [R2, #0x20]; , Ro = menory [0x1020] ; RI = memory [0x1024] 10) Table Branch Byte and Table Branch Halfword -> TBB and TBH are for implementing branch tables -> The TBB instruction uses a branch table of bytedize -> TBH uses a branch table of half word offset. Branch range for TBB is (2x255)+4 = 514 Branch range for TBH is (2x65535)+4 = 131074 Syntax TBB. W [Rn, Rm]

TBB. W [Rn, Rm] Rn = base memory offset

TBB. W [PC, RD]; Rm = branch table index

; when executing this, Pc equal branch table

#### MEMORY NAPPING

The costex - M3 processon has a fixed memory map. This makes it easier to post software from one cortex - M3 product to another.

- -> Components such as Nested Vector Guterrupt Controller (NVIC) and Memory Protection unit (MPV) have the same memory locations in all Cortex - M3 products.

- -> Some of the memory locations are allocated for private periphetals such as debugging components They include

- · Fetch Patch and Breakpoint Unit (FPB)

- · Data watchpoint and Trace Unit (DWT)

- · Instrumentation Trace Macrocell (ITH)

- · Embedded Trace Macrocell (ETH)

- · Trace Port Interface Unit (TPIU)

- · ROM Table

The coertex-M3 processes has a stotal of &GB of address upace. Program code can be located in the code siegien, the Static Random Access Memory (SRAM) region or the external RAM region

PTOO

| OVERDOSECOO                 |                               |         |                         | X FFFFFFF                               |

|-----------------------------|-------------------------------|---------|-------------------------|-----------------------------------------|

| OKED OFF DOO                | ROM teuble                    | 1       |                         |                                         |

| OXE DOFEFF                  | External private perputat ous | 1       | Vendon Specific         |                                         |

| 0XE 904-5000                | ETM                           |         | Private perigheral bus: | OXE DIBODDO                             |

| OXE DOTOE                   | TDIV                          |         | Debug/external          |                                         |

| OXEOU3FFF                   |                               |         |                         | OXED040000                              |

| OX E DOOF DOO               | Researed                      |         | Private peripheral      |                                         |

| 0XEDODED00                  | NVIC                          |         | bus: Internal           |                                         |

| 0X€000 DFFF                 | Reserved                      |         |                         | OXEDODOOOO                              |

|                             | FPB                           | /       |                         | *************************************** |

| DXE 0002000                 | DWT                           | /       | External device         |                                         |

| OXE0001 000                 | TTM                           | /       |                         |                                         |

| OX + 3 FFFFFF               |                               | 4       | 1618                    | OX ADDODOO                              |

| 0X4 2000000<br>0X4 1 FFFFFF | Rit I and I                   |         | External RAM            | OX 9 FFFFFF                             |

| 0X40100000                  | 251 1 1                       |         | 1618                    | 0x60000000                              |

| OX 4-00000000               | IMB Bit sand region           | 1       | Partalanal.             |                                         |

|                             |                               | 1       | Peripherals             | 0x40000000                              |

| DX 23 FFFFFF                |                               |         |                         | OX 3FFF FFF                             |

|                             | Bit-band alias                |         | SRAM                    |                                         |

| 0X21FFFFF                   | 32 M /S                       |         | 0.561B                  | OX 2 0000000                            |

| OK 2 0100000                |                               | /       |                         | OX ) FFFFFF                             |

| 6x 2 000 000 0              | IMB Bit-band region           |         | Code                    | 0×00000000                              |

|                             |                               |         |                         |                                         |

|                             | CORTEX -M3 Pre                | defined | Memory Map              |                                         |

| -> The s                    | RAM memory siano              | de in   | Los connection          | internal                                |

| RAM .                       | Access to this                | region  | 14 5000 1               | 1                                       |

| system                      | interface bus . 9,            | n this  | as carried ou           | t mathe                                 |

| is defi                     | ned as a bit-band             | alia    | signou la 32 M          | 18 range                                |

| -> Ano+                     | her 0.5 G1 B block            | o.J     | ddreas raise            | 200 + 1                                 |

| to ou                       | her 0.5 G1 B block            | total   | wess range is           | allocated                               |

| region                      | chip peripherals. I           | nsmer   | ion execution s         | in this                                 |

| 0                           | munea.                        |         |                         |                                         |

- -> Two slots of 1618 memory opace are allowed for external RAM and external devices

- some last 0.5 G1B memory is for the system level components, internal peripheral buses, external peripheral buses, external peripheral buses and vendor specific system peripherals.

- -> There are two segments of the private peripheral bus (PPB):

- \* Advanced High-Performance Bus (AHB)

- \* Advance Peripheral Bus (APB)

The NVIC is located in a memory region called the system control space (505)

-> The Cortex-M3 processor also comes with an optional MPU.

System level Block: (Repeated)

9t is divided into three blocks:

1. Private peripheral Bus interface.

-> NVIC - combol or monitors the 256 inferrupts

-> FPB - Flash Patch Break point

This is mainly used for debugging break point means you can start executing the code from that point. Here we case inserting the break point at the place we want to debug.

2. Private Peripheral bus debug/External

-> ETM: Embedded Trace macrocell

-> TPIV: Trace point Interface unit

- > ROM table

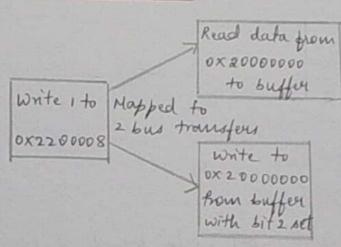

#### BIT -BAND OPERATIONS

Bit Band operation support allows a single lead store operation to access (read/write) to a single data bit.

In the CORTEX-M3 this is supported in two predefined memory segions called bit-band regions - some of them is docated in the first IMB of the SRAM and the other is located in the first IMB of the Peripheral region.

- -> These two memory regions can be accessed like mormal memory, but they can also be accessed via a separate memory region called the bit-band-alias.

- when the bit band alias address is used, each individual bit can be accessed separately in the least significant bit (LSB) of each word-aligned address.

Ex;

To set bit 2 in word data in address 0x20000000, instead of using three instructions to read the data, set the bit and then write back the result, this task can be carried out by a single instruction as shown in figure below

PTOS

#### Example:

Assembler sequence to write a drit with & without bit-Band

Without 6it-band

LDR RO, =0x20000000; Sehip add

LDR RI, [RO]; Read

ORR.W RI, #0x4; Modify bit

STR RI, [RO]; write back

with bit-band

LDR RO, = 0x22000008; setup add

NOV RI, #1 ; setup data

STR RI, [RO] ; write

#### figure:

Bit Accesses to Bit-Bound Region via the Bit-Bound Hias

Without bit-band

with bit-band

within the 6it-band region, each word is represented by an LSB of 32 words in the 6it-band alias address

- -> when the bit-band alias address is accessed, the address is ounapped into a bit-band address.

- -) Fast sead operations, the word is read and the chosen bit location is shifted to LSB of the read return data.

- -) For write operation, the written left data are shifted to the required sit position and a

There are 2 rights of memory for bit band operations:

- · 0x20000000 0x200FFFFF (SRAM, IMB)

- · OX40000000 OX400FFFFF (Peripherals, IMB)

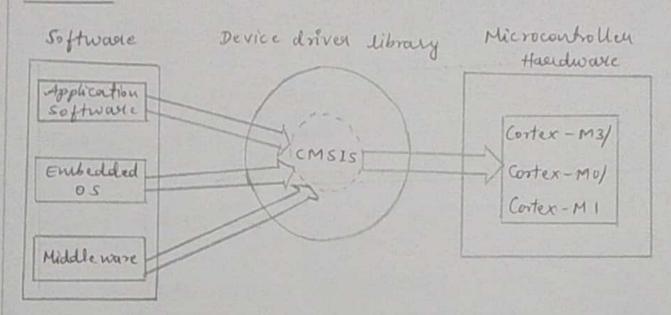

#### CMSIS

-> CMS 15 provides a standardized access interface for

The CMSIS was developed by ARM to allow users of the Costex-M3 unicrocontrollers to gain the most benefit from all these software solutions and to allow them to develop their embedded application quickly and reliably.

#### The aim of CMSIS are to:

- · improve software portability and revisability · enable software solution marks to

- products that can work seamlessly with device libraries from various silicon vendors.

- · allow combedded developeus to develop software quicken with an easy to use of standardised software interface.

- · allows embedded software to be used on multiple compute products.

### ORGIANISATION OF CMSIS

The CMSIS is diveded into multiple layers as follows

- -> Core Peripheral layer

- · Name définitions, address définitions of helpen functions to access core régisters of core peripherals.

- -> Middle wale Access layer

- · Jargeted communication interfaces include Ethernet,

- tasks on any coster inicsocontrollers that suppost the seguired communication interface.

- -> Device Peripheral Access layer (MCV specific)

- · Name definition, address definition of driven code to access peripherals.

- -> Access Functions for Peripherals (Mcu specific)

- · Optional additional helper function for peripherals

- The main benefits of CMSIS is

- \* much better software postability and reusability

\* Besides easy migration between different cortex-M3

microcontrollers, it also allows software to be quickly

ported to cortex-M3 and other cortex-M processors

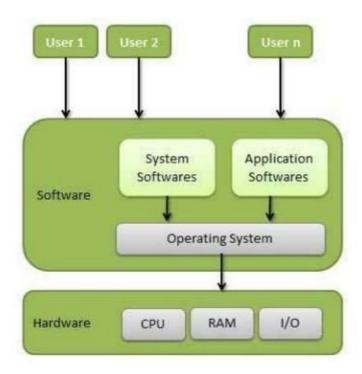

- reducing time to market CMSIS STRUCTURE Application Code Usea Real-time Middleware RTOS Keinel Components Core Peripherals Middlemare Peripheral functions access function CMS15 Perpheral registers of interrupt Jexception vector definition SYSTICK Processor NVIC Debug/ other MCU RTDS Kesund Network peripher vector inter - supt controller Times intenface Cortex - M Processor. ASSEMBLY AND G LANGUAGE PROGRAMMING Using C ! Programming in c with the cortex-M3 processor is made easier as most micro controller wandons provide device direce libraries written in c to control peripherals. -> Since modern C-compilers can generate very efficient code it is better to program in a than spending a lot of time to try to develop complex noutines in assembly language which is error prone

and less posetable

# Using Assembly

Mosny Assembler, we might be able to get the best optimization we want, though "it might increase our development time and it could also be easy to make mistakes.

Implemented in assembly language as follows:

Trunctions that cannot be implemented in c, such as direct manipulation of stack data on special instructions that cannot be generated by the compiler in mormal code

-> Timing-critical routines.

-> Tight memory requirements, causing pant of the program to be written in assembly to get the smallest memory size

In vaccious situations, assembly code and the c Program interact, they are:

- -> when embedded assembly is used in Cprogram code

- -> when c program code calls a function on subrouti -ne implemented in assembler in a separate line.

- or subscoutine.

```

Example of a Simple c program

# define LED + (( volatile unsigned int +) ( ox DFF F0000))

int main (void)

int 1; 1x loop counter for delay function +1

volatile int 9; 1* dumny volatile raviable to

prevent c compiler from optimize

the delay away */

while (i)

LED = 0x00; /* toogle LED*/

for ( i=0; i<10; i++) (j=0; } /* delay */

LED = 0x01; /+ toogle LED+/

for (i=0; i<10; i++) {j=0; }/* delay*1

return o;

```

### <u>.DEFINITION OF AN EMBEDDED SY STEM</u>

An embedded system is a combination of 3 types of components: a. Hardware b. Software c. Mechanical Components and it is supposed to do one specific task only.

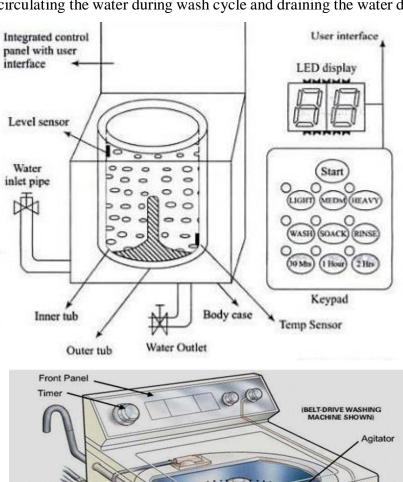

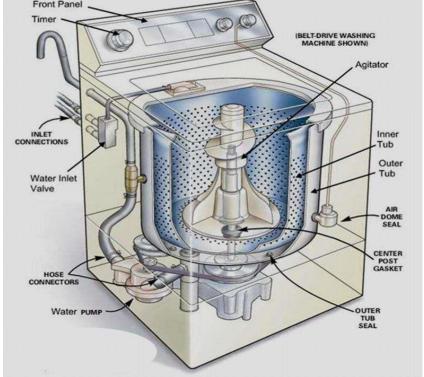

### Example 1: Washing Machine

• A washing machine from an embedded systems point of view has: a. Hardware: Buttons, Display & buzzer, electronic circuitry. b. Software: It has a chip on the circuit that holds the software which drives controls & monitors the various operations possible. c. Mechanical Components: the internals of a washing machine which actually wash the clothes control the input and output of water, the chassis itself.

# Example 2: Air Conditioner

- An Air Conditioner from an embedded systems point of view has: a. Hardware: Remote, Display & buzzer, Infrared Sensors, electronic circuitry. b. Software: It has a chip on the circuit that holds the software which drives controls & monitors the various operations possible. The software monitors the external temperature through the sensors and then releases the coolant or suppresses it. c. Mechanical Components: the internals of an air conditioner the motor, the chassis, the outlet, etc An embedded system is designed to do a specific job only.

- Example: a washing machine can only wash clothes, an air conditioner can control the temperature in the room in which it is placed.

The hardware & mechanical components will consist all the physically visible things that are used for input, output, etc. An embedded system will always have a chip (either• microprocessor or microcontroller) that has the code or software which drives the system

### EMBEDDED SYSTEM & GENERAL PURPOSE COMPUTER

The Embedded System and the General purpose computer are at two extremes. The embedded system is designed to perform a specific task whereas as per definition the general purpose computer is meant for general use. It can be used for playing games, watching movies, creating software, work on documents or spreadsheets etc. Following are certain specific points that differenciates between embedded systems and general purpose computers:

| Criteria                 | General Purpose<br>Computer                                                                             | Embedded system                                    |  |

|--------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| Contents                 | It is combination of generic hardware and a general purpose OS for executing a variety of applications. | purpose hardware and embedded OS for executing     |  |

| Operating<br>System      | It contains general purpose operating system                                                            | It may or may not contain operating system.        |  |

| Alterations              | Applications are alterable by the user.                                                                 | Applications are non-alterable by the user.        |  |

| Key factor               | Performance" is key factor.                                                                             | Application specific requirements are key factors. |  |

| Power<br>Consumpti<br>on | More                                                                                                    | Less                                               |  |

| Response<br>Time         | Not Critical                                                                                            | Critical for some applications                     |  |

### **CLASSIFICATION OF EMBEDDED SYSTEMS**

The classification of embedded system is based on following criteria's:

- On generation

- On complexity & performance

- On deterministic behavior

- On triggering

# > On generation:

- 1. First generation (1G):

- Built around 8bit microprocessor & microcontroller.

- Simple in hardware circuit & firmware developed.

- Examples: Digital telephone keypads.

- 2. Second generation (2G):

- Built around 16-bit μp & 8-bit μc.

- They are more complex & powerful than 1G μp & μc.

• Examples: SCADA systems

# 3. Third generation (3G):

- Built around 32-bit μp□& 16-bit μc.

- Concepts like Digital Signal Processors (DSPs), Application Specific Integrated Circuits(ASICs) evolved. Examples: Robotics, Media, etc.

# 4. Fourth generation:

- Built around 64-bit μp & 32-bit μc.

- The concept of System on Chips (SoC), Multicore Processors evolved.

- Highly complex & very powerful. Examples: Smart Phones.

# ➤ On complexity & performance:

### 1. Small-scale:

- > Simple in application need

- > Performance not time-critical.

- > Built around low performance & low cost 8 or 16 bit μp/μc. Example: an electronic toy

### 2. Medium-scale:

- > Slightly complex in hardware & firmware requirement.

- $\triangleright$  Built around medium performance & low cost 16 or 32 bit  $\mu p/\mu c$ .

- > Usually contain operating system.

- > Examples: Industrial machines.

### 3. Large-scale:

- ➤ Highly complex hardware & firmware.

- > Built around 32 or 64 bit RISC μp/μc or PLDs or Multicore-Processors.

- Response is time-critical.

- > Examples: Mission critical applications.

#### > On deterministic behavior:

- This classification is applicable for "Real Time" systems.

- ➤ The task execution behavior for an embedded system may be deterministic or non-deterministic.

- ➤ Based on execution behavior Real Time embedded systems are divided into Hard and Soft.

# On triggering

- Embedded systems which are "Reactive" in nature canbe based on triggering.

- Reactive systems can be:

- > Event triggered

- > Time triggered

### APPLICATION OF EMBEDDED SYSTEM

The application areas and the products in the embedded domain are countless.

- 1. Consumer Electronics: Camcorders, Cameras.

- 2. Household appliances: Washing machine, Refrigerator.

- 3. Automotive industry: Anti-lock breaking system(ABS), engine control.

- 4. Home automation & security systems: Air conditioners, sprinklers, fire alarms.

- 5. Telecom: Cellular phones, telephone switches.

- 6. Computer peripherals: Printers, scanners.

- 7. Computer networking systems: Network routers and switches.

- 8. Healthcare: EEG, ECG machines.

- 9. Banking & Retail: Automatic teller machines, point of sales.

- 10. Card Readers: Barcode, smart card readers.

# PURPOSE OF EMBEDDED SYSTEM

- 1. Data Collection/Storage/Representation

- ➤ Embedded system designed for the purpose of data collection performs acquisition of data from the external world.

- ➤ Data collection is usually done for storage, analysis, manipulation and transmission.

- > Data can be analog or digital.

- Embedded systems with analog data capturing techniques collect data directly in the form of analog signal whereas embedded systems with digital data collection

mechanism converts the analog signal to the digital signal using analog to digital converters.

- ➤ If the data is digital it can be directly captured by digital embedded system.

- ➤ A digital camera is a typical example of an embedded System with data collection/storage/representation of data.

- ➤ Images are captured and the captured image may be stored within the memory of the camera. The captured image can also be presented to the user through a graphic LCD unit.

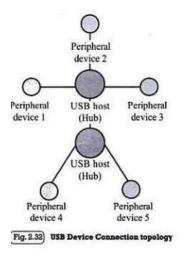

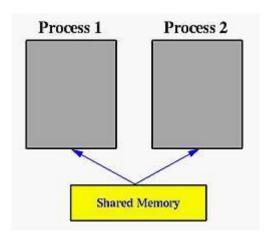

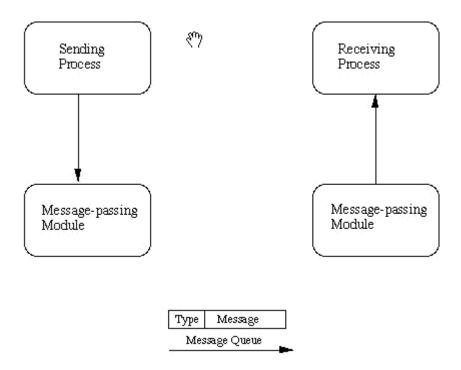

### 2. Data communication

- ➤ Embedded data communication systems are deployed inapplications from complex satellite communication to simple home networking systems.

- ➤ The transmission of data is achieved either by a wire-lin medium or by a wire-less medium. Data can either be transmitted by analog means or by digital means.

- ➤ Wireless modules-Bluetooth, Wi-Fi.

- ➤ Wire-line modules-USB, TCP/IP.

- ➤ Network hubs, routers, switches are examples of dedicated data transmission embedded systems.

### 3. Data signal processing

- ➤ Embedded systems with signal processing functionalities are employed in applications demanding signal processing like speech coding, audio video codec, transmission applications etc.

- ➤ A digital hearing aid is a typical example of an embedded system employing data processing. Digital hearing aid improves the hearing capacity of hearing impaired person.

### 4. Monitoring

- ➤ All embedded products coming under the medical domain are with monitoring functions. Electro cardiogram machine is intended to do the monitoring of the heartbeat of a patient but it cannot impose control over the heartbeat.

- ➤ Other examples with monitoring function are digital CRO, digital multi-meters, and logic analyzers.

#### 5. Control

- A system with control functionality contains both sensors and actuators Sensors are connected to the input port for capturing the changes in environmental variable and the actuators connected to the output port are controlled according to the changes in the input variable.

- ➤ Air conditioner system used to control the room temperature to a specified limit is a typical example for CONTROL purpose.

- 6. Application specific user interface

- ➤ Buttons, switches, keypad, lights, bells, display units etc are application specific user interfaces.

- Mobile phone is an example of application specific user interface.

- In mobile phone the user interface is provided through the keypad, system speaker, vibration alert etc.

### CORE OF EMBEDDED SYSTEMS

Embedded systems are domain and application specific and are built around a central core. The core of the embedded system falls into any of the following categories:

- 1. General purpose and Domain Specific Processors Microprocessors Microcontrollers Digital Signal Processors.

- 2. Application Specific Integrated Circuits. (ASIC)

- 3. Programmable logic devices(PLD's)

- 4. Commercial off-the-shelf components (COTs)

### GENERAL PURPOSE AND DOMAIN SPECIFIC PROCESSOR.

- Almost 80% of the embedded systems are processor/controller based.

- The processor may be microprocessor or a microcontroller or digital signal processor, depending on the domain and application.

### **Microprocessors**

- A microprocessor is a silicon chip representing a central processing unit.

- A microprocessor is a dependent unit and it requires the combination of other hardware like memory, timer unit, and interrupts controller, etc. for proper functioning.

Developers of microprocessors.

- ➤ Intel Intel 4004 November 1971(4-bit).

- Intel Intel 4040. o Intel Intel 8008 April 1972.

- Intel Intel 8080 April 1974(8-bit).

- Motorola Motorola 6800.

- Intel Intel 8085 1976.

- Zilog Z80 July 1976.

Architectures used for processor design are Harvard or VonNeumann.

| l                             | Harvard architecture                                              | Von-Neumann architecture                                         |  |

|-------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|--|

|                               | ☐ It has separate buses for instruction as well as data fetching. | ☐ It shares single common bus for instruction and data fetching. |  |

|                               | ☐ Easier to pipeline, so high performance can be achieve.         | ☐ Low performance as compared to Harvard architecture.           |  |

| l                             | Comparatively high cost.                                          | ☐ It is cheaper.                                                 |  |

| l                             | ☐ Since data memory and                                           | ☐ Accidental corruption of                                       |  |

| l                             | program memory are stored                                         | program memory may occur if                                      |  |

| l                             | physically in different locations,                                | data memory and program                                          |  |

| l                             | no chances exist for accidental                                   | memory are stored physically                                     |  |

| corruption of program memory. |                                                                   | in the same chip,                                                |  |

RISC and CISC are the two common Instruction Set Architectures (ISA) available for processor design.

| RISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RISC  Reduced Instruction Set Computing It contains lesser number of instructions. Instruction pipelining and increased execution speed. Orthogonal instruction set(allows each instruction to operate on any register and use any addressing mode. Operations are performed on registers only, only memory operations are load and store. A larger number of registers are available.  Programmer needs to write more code to execute a task since instructions are simpler ones. | CISC  ☐ Complex Instruction Set Computing ☐ It contains greater number of instructions. ☐ Instruction pipelining feature does not exist. ☐ Non-orthogonal set(all instructions are not allowed to operate on any register and use any addressing mode. ☐ Operations are performed either on registers or memory depending on instruction. ☐ The number of general purpose registers are very limited. ☐ Instructions are like macros in C language. A programmer can achieve the desired functionality with a single instruction which in turn provides the effect of using more simpler single |  |

| ☐ It is single, fixed length instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                          | instruction in RISC.  ☐ It is variable length instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

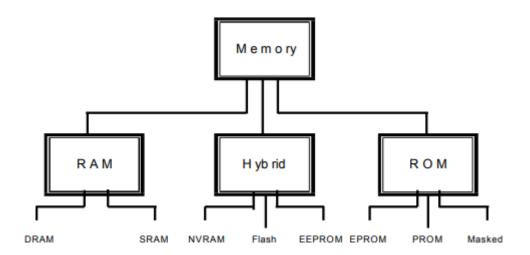

#### **Microcontrollers**

- A microcontroller is a highly integrated chip that contains aCPU, scratch pad RAM, special and general purpose register arrays, on chip ROM/FLASH memory for program storage, timer and interrupt control units and dedicated I/O ports.

- Texas Instrument's TMS 1000 Is considered as the world's first microcontroller.

- Some embedded system application require only 8 bit controllers whereas some requiring superior performance and computational needs demand 16/32 bit controllers.

- The instruction set of a microcontroller can be RISC or CISC.

- Microcontrollers are designed for either general purpose application requirement or domain specific application requirement.

### **Digital Signal Processors**

- DSP are powerful special purpose 8/16/32 bit microprocessor designed to meet the computational demands and power constraints of today's embedded audio, video and communication applications. DSP are 2 to 3 times faster than general purpose microprocessors in signal processing applications.

- This is because of the architectural difference between DSP and general purpose microprocessors.

- DSPs implement algorithms in hardware which speeds up the execution whereas general purpose processor implement the algorithm in software and the speed of execution depends primarily on the clock for the processors.

- DSP includes following key units:

- i. Program memory: It is a memory for storing the program required by DSP to process the data. ii. Data memory: It is a working memory for storing temporary variables and data/signal to be processed.

- iii. Computational engine: It performs the signal processing in accordance with the stored program memory computational engine incorporated many specialized arithmetic units and each of them operates simultaneously to increase the execution speed. It also includes multiple hardware shifters for shifting operands and saves execution time.

- iv. I/O unit: It acts as an interface between the outside world and DSP. It is responsible for capturing signals to be processed and delivering the processed signals.

- Examples: Audio video signal processing, telecommunication and multimedia applications. SOP(Sum of Products) calculation, convolution, FFT(Fast Fourier Transform), DFT(Discrete Fourier Transform), etc are some of the operation performed by DSP.

# **Application Specific Integrated Circuits. (ASIC)**

- ASICs is a microchip design to perform a specific and unique applications.

- Because of using single chip for integrates several functions there by reduces the system development cost.

- Most of the ASICs are proprietary (which having some trade name) products, it is referred as Application Specific Standard Products(ASSP).

- As a single chip ASIC consumes a very small area in the total system.

- Thereby helps in the design of smaller system with high capabilities or functionalities.

- The developers of such chips may not be interested in revealing the internal detail of it.

# Programmable logic devices(PLD's)

- A PLD is an electronic component. It used to build digital circuits which are reconfigurable.

- A logic gate has a fixed function but a PLD does not have a defined function at the time of manufacture.

- PLDs offer customers a wide range of logic capacity, features, speed, voltage characteristics. PLDs can be reconfigured to perform any number of functions at any time.

- A variety of tools are available for the designers of PLDs•which are inexpensive and help to develop, simulate and test the designs.

PLDs having following two major types.

- 1) CPLD(Complex Programmable Logic Device): CPLDs offer much smaller amount of logic up to 1000 gates.

- 2) FPGAs(Field Programmable Gate Arrays): It offers highest amount of performance as well as highest logic density, the most features.

**Advantages of PLDs**: - 1) PLDs offer customer much more flexibility during the design cycle.

- 2) PLDs do not require long lead times for prototypes or production parts because PLDs are already on a distributors shelf and ready for shipment.

- 3) PLDs can be reprogrammed even after a piece of equipment is shipped to a customer

### **Commercial off-the-shelf components(COTs)**

- 1) A Commercial off the Shelf product is one which is used 'asis'.

- 2) The COTS components itself may be develop around a general purpose or domain specific processor or an ASICs or a PLDs.

- 3) The major advantage of using COTS is that they are readily available in the market, are chip and a developer can cut down his/her development time to a great extent

4) The major drawback of using COTS components in embedded design is that the manufacturer of the COTS component may withdraw the product or discontinue the production of the COTS at any time if rapid change in technology occurs.

# **Advantages of COTS:**

- 1) Ready to use

- 2) Easy to integrate

- 3) Reduces development time

# **Disadvantages of COTS:**

- 1) No operational or manufacturing standard (all proprietary)

- 2) Vendor or manufacturer may discontinue production of a particular COTS product

### **SENSORS & ACTUATORS**

### Sensor

- A Sensor is used for taking Input

- It is a transducer that converts energy from one form to another for any measurement or control purpose Ex. A Temperature sensor

#### **Actuator**

Actuator is used for output. It is a transducer that may be either mechanical or electrical which converts signals to corresponding physical actions.

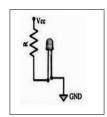

### **LED (Light Emitting Diode)**

LED is a p-n junction diode and contains a CATHODE and ANODE For functioning the anode is connected to +ve end of power supply and cathode is connected to -ve end of power supply. The maximum current flowing through the LED is limited by connecting a RESISTOR in series between the power supply and LED as shown in the figure below

There are two ways to interface an LED to a microprocessor/microcontroller:

- 1. The Anode of LED is connected to the port pin and cathode to Ground: In this approach the port pin sources the current to the LED when it is at logic high(ie. 1).

- 2. The Cathode of LED is connected to the port pin and Anode to Vcc: In this approach the port pin sources the current to the LED when it is at logic high (ie. 1). Here the port pin sinks the current and the LED is turned ON when the port pin is at Logic low (ie. 0)

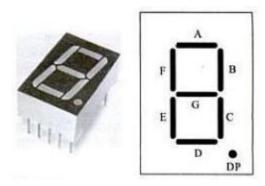

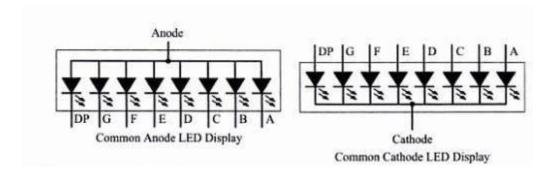

# 7-segment display:

A seven-segment display (SSD), or seven-segment indicator, is a form of electronic display device for displaying decimal numerals that is an alternative to the more complex dot matrix displays. Seven-segment displays are widely used in digital clocks, electronic meters, basic calculators, and other electronic devices that display numerical information.

The seven elements of the display can be lit in different combinations to represent the Arabic numerals. Often the seven segments are arranged in an *oblique* (slanted) arrangement, which aids readability. In most applications, the seven segments are of nearly uniform shape and size (usually elongated hexagons, though trapezoids and rectangles can also be used), though in the case of adding machines, the vertical segments are longer and more oddly shaped at the ends in an effort to further enhance readability.

The numerals 6 and 9 may be represented by two different glyphs on seven-segment displays, with or without a 'tail'. [2][3] The numeral 7 also has two versions, with or without segment F. [4]

The seven segments are arranged as a rectangle of two vertical segments on each side with one horizontal segment on the top, middle, and bottom. Additionally, the seventh segment bisects the rectangle horizontally. There are also fourteen-segment displays and sixteen-segment displays (for full alphanumerics); however, these have mostly been replaced by dot matrix

displays. Twenty-two segment displays capable of displaying the full ASCII character set<sup>[5]</sup> were briefly available in the early 1980s, but did not prove popular.

The segments of a 7-segment display are referred to by the letters A to G, where the optional decimal point (an "eighth segment", referred to as DP) is used for the display of non-integer numbers.

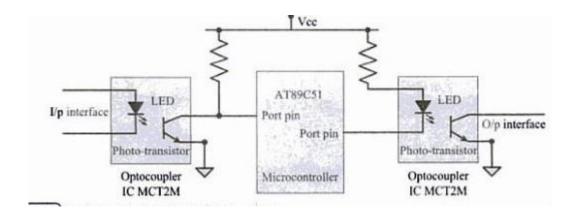

# **Optical coupler:**

An optical coupler, also called opto-isolator, optocoupler, opto coupler, photocoupler or optical isolator, is a passive optical component that can combine or split transmission data (optical power) from optical fibers. It is an electronic device which is designed to transfer electrical signals by using light waves in order to provide coupling with electrical isolation between its input and output. The main purpose of an optocoupler is to prevent rapidly changing voltages or high voltages on one side of a circuit from distorting transmissions or damaging components on the other side of the circuit. An optocoupler contains a light source often near an LED which converts electrical input signal into light, a closed optical channel and a photosensor, which detects incoming light and either modulates electric current flowing from an external power supply or generates electric energy directly. The sensor can either be a photoresistor, a silicon-controlled rectifier, a photodiode, a phototransistor or a triac.

# **Applications for Optocouplers:**

Photoresistor-based opto-isolators are the slowest type of optocouplers, but also the most linear isolators and are used in the audio and music industry. Most opto-isolators available use bipolar silicon phototransistor sensors and reach medium data transfer speed, which is enough for applications like electroencephalography. High speed opto-isolators are used in computing and communications applications. Other industrial applications include photocopiers, industrial automation, professional light measurement instruments and auto-exposure meters.

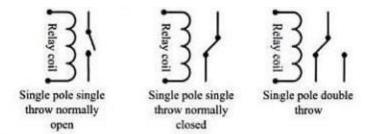

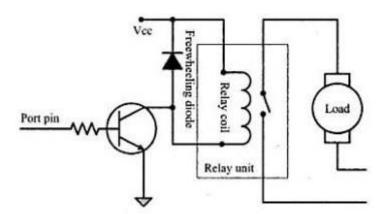

### Relay:

A relay is an electrically operated switch. Many relays use an electromagnet to mechanically operate a switch, but other operating principles are also used, such as solid-state relays. Relays are used where it is necessary to control a circuit by a separate low-power signal, or where several circuits must be controlled by one signal. The first relays were used in long distance telegraphcircuits as amplifiers: they repeated the signal coming in from one circuit and retransmitted it on another circuit. Relays were used extensively in telephone exchanges and early computers to perform logical operations. A type of relay that can handle the high power required

to directly control an electric motor or other loads is called a contactor. Solid-state relays control power circuits with no moving parts, instead using a semiconductor device to perform switching. Relays with calibrated operating characteristics and sometimes multiple operating coils are used to protect electrical circuits from overload or faults; in modern electric power systems these functions are performed by digital instruments still called "protective relays".

Magnetic latching relays require one pulse of coil power to move their contacts in one direction, and another, redirected pulse to move them back. Repeated pulses from the same input have no effect. Magnetic latching relays are useful in applications where interrupted power should not be able to transition the contacts.

Magnetic latching relays can have either single or dual coils. On a single coil device, the relay will operate in one direction when power is applied with one polarity, and will reset when the polarity is reversed. On a dual coil device, when polarized voltage is applied to the reset coil the contacts will transition. AC controlled magnetic latch relays have single coils that employ steering diodes to differentiate between operate and reset commands.

#### **Buzzer:**

A **buzzer** or **beeper** is an audio signalling device, which may be mechanical, electromechanical, or piezoelectric (*piezo* for short). Typical uses of buzzers and beepers include alarm devices, timers, and confirmation of user input such as a mouse click or keystroke.

### **Types of Buzzers**

There are several different kinds of buzzers. At Future Electronics we stock many of the most common types categorized by Type, Sound Level, Frequency, Rated Voltage, Dimension and Packaging Type. The parametric filters on our website can help refine your search results depending on the required specifications.

The most common sizes for Sound Level are 80 dB, 85 dB, 90 dB and 95 dB. We also carry buzzers with Sound Level up to 105 dB. There are several types available including Electro-Acoustic, Electromagnetic, Electromechanic, Magnetic and Piezo, among others.

# **Applications for Buzzers:**

Typical uses of buzzers include:

- Alarm devices

- Timers

- Confirmation of user input (ex: mouse click or keystroke)

- Electronic metronomes

- Annunciator panels

- Game shows

- Sporting events

- Household appliances

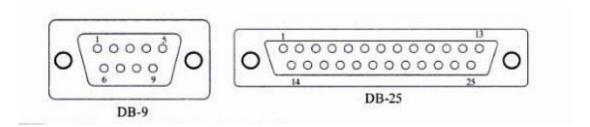

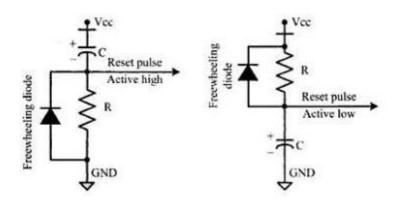

### **Push button switch:**